# User's Guide

Publication number E2480-97002 July 1998

© Copyright Hewlett-Packard Company 1994-1998

All Rights Reserved

For Safety information, Warranties, and Regulatory information, see the pages behind the index.

# Solutions for the Motorola CPU32

# HP Solutions for the Motorola CPU32—At a Glance

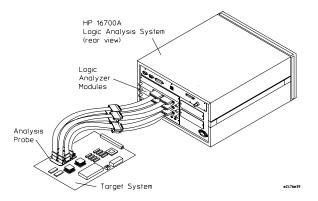

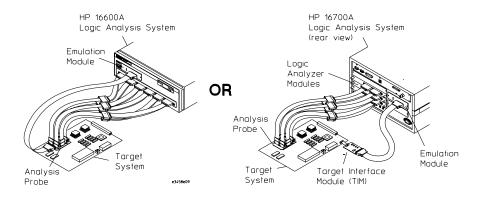

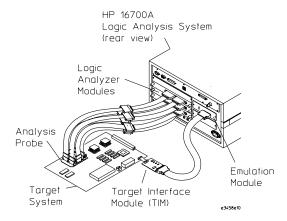

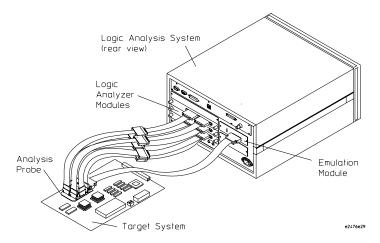

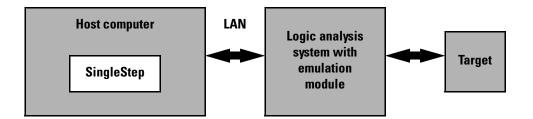

This manual describes several ways to connect an HP logic analysis system to your target system. These connections use an analysis probe, plus an emulation module (for an emulation solution).

# **Analysis Probe**

The analysis probe connects your logic analyzer to your target system for state and timing analysis. The analysis probe can be used with an HP 16600A/700A-series logic analysis system or with other HP logic analyzers.

The analysis probe can be purchased alone, or as part of an emulation solution.

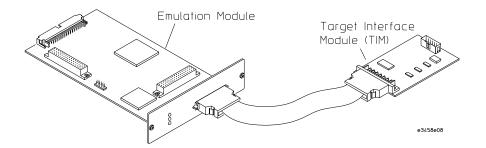

# **Emulation Module and Target Interface Module**

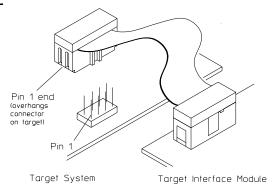

The emulation module plugs into your HP 16600A/700A-series logic analysis system frame. The emulation module lets you use the target processor's built-in background debugging features, including run control and access to registers and memory. A high-level source debugger can use the emulation module to debug code running on the target system. You can connect the emulation module to the analysis probe or you can connect it to a debug port on the target system through the provided target interface module (TIM).

#### **Emulation Solution**

The emulation solution includes an analysis probe, an emulation module, cables and adapters, and the HP B4620B Source Correlation Tool Set (for analyzing high-level source code). This solution is designed to be used with an HP 16600A/700A-series logic analysis system.

# In This Book

This book documents the following products:

| Analysis Probe                             |                       |                                                |  |

|--------------------------------------------|-----------------------|------------------------------------------------|--|

| Processor supported                        | Product ordered       | Includes                                       |  |

| 68331, 68332, 68334, 68335<br>132-pin PQFP | HP E9589A Option #002 | HP E2480A analysis probe and inverse assembler |  |

| 68331, 68332<br>144-pin TQFP               | HP E9589A Option #003 | HP E2480A analysis probe and inverse assembler |  |

| 68336, 68376<br>160-pin QFP                | HP E9596A Option #002 | HP E2480A analysis probe and inverse assembler |  |

| Emulation Solution                         |                      |                                                                                                                                                        |  |  |

|--------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Processor supported                        | Product ordered      | Includes                                                                                                                                               |  |  |

| 68331, 68332, 68334, 68335<br>132-pin PQFP | HP 9489A Option #002 | HP E2480A analysis probe, inverse<br>assembler, HP 16610A emulation module,<br>target interface module (TIM), HP B4620B<br>Source Correlation Tool Set |  |  |

| 68331, 68332<br>144-pin ΤΩFP               | HP 9489A Option #003 | HP E2480A analysis probe, inverse assembler, HP 16610A emulation module, target interface module (TIM), HP B4620B Source Correlation Tool Set          |  |  |

| 68336, 68376<br>160-pin QFP                | HP 9496A Option #002 | HP E2480A analysis probe, inverse<br>assembler, HP 16610A emulation module,<br>target interface module (TIM), HP B4620B<br>Source Correlation Tool Set |  |  |

HP Solutions for the Motorola CPU32—At a Glance 2 In This Book 4

#### 1 Overview

Overview 16

Setup Checklist 17

Setup Assistant 19

Analysis Probe 20

Equipment supplied 20

Minimum equipment required 22

Additional equipment supported 22

Logic analyzers supported 23

Logic analyzer software version requirements 24

Emulation Module 25

Equipment supplied 25

Minimum equipment required 26

Emulation Solution 27

Additional Information Sources 28

#### 2 Installing Software

Installing Software 30

Installing and loading 30

What needs to be installed 31

To install the software from CD-ROM

(HP 16600A/700A) 32

To list software packages which are installed (HP 16600A/700A) 33

To install software on other logic analyzers 33

# 3 Connecting and Configuring the Analysis Probe

| Connecting and Configuring the Analysis Probe 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Target System Requirements 37 Analysis probe—circuit board dimensions 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Power-on/Power-off Sequence 39 To power on HP 16600A and HP 16700A-series logic analysis systems 39 To power on all other logic analyzers 39 To power off 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Connecting the Analysis Probe to the Target System 42 To connect the transition board 43 To connect the analysis probe to the probe adapter 44 Connecting the probe adapter to the target system 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Connecting the Analysis Probe to the Logic Analyzer 49  To connect the high-density termination cables to the analysis probe 50  Connecting the high-density cables to the logic analyzer 51  To connect to the HP 16600A logic analyzer 52  To connect to the HP 16601A logic analyzer 54  To connect to the HP 16602A logic analyzer 56  To connect to the HP 16603A logic analyzer 58  To connect to the HP 16550A analyzer 60  To connect to the HP 16554/55A/56/57D analyzers 63  To connect to the HP 1660A/AS/C/CS/CP logic analyzers 65  To connect to the HP 1661A/AS/C/CS/CP logic analyzers 67  To connect to the HP 1662A/AS/C/CS/CP logic analyzers 69  To connect to the HP 1670A/D logic analyzer 71  To connect to the HP 1671A/D logic analyzer 73  To connect to the HP 1672A/D logic analyzer 75 |

| Configuring the Analysis Probe 77 To set the ID switches 78 To interpret the LEDs 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Configuring the analysis probe for address reconstruction 81 To configure with a debugger 81 To configure with a logic analysis system 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Configuring the Logic Analysis System 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

6 Solutions for CPU32

To load configuration and inverse assembler files—HP 16600/700 logic analysis

systems 84

To load configuration files—other logic analyzers 85

#### 4 Analyzing the CPU32 with a Logic Analyzer

Analyzing the CPU32 with a Logic Analyzer 90

Modes of Operation 91 State mode 91 Timing mode 91

Logic Analyzer Configuration 92

Trigger specification 92

Format menu 92

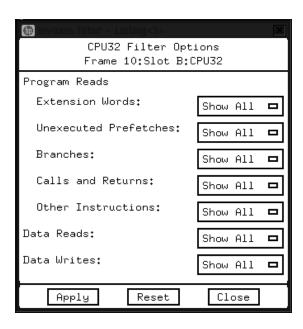

To qualify stored data 98

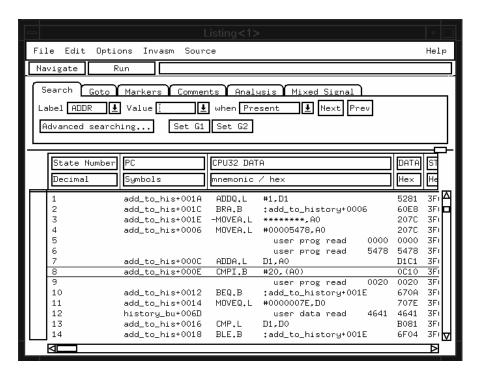

Using the Inverse Assembler 99

To display captured state data 99

To align the inverse assembler 101

Inverse assembler output format 102

To use the Invasm menu 104

Inverse assembler error messages 106

### 5 Symbols and Source Code in the Analyzer

Symbols and Source Code in the Analyzer 108

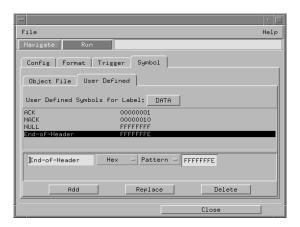

User-Defined Symbols 109 Predefined CPU32 Symbols 109

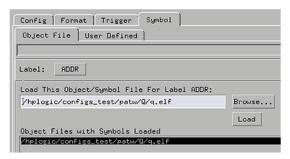

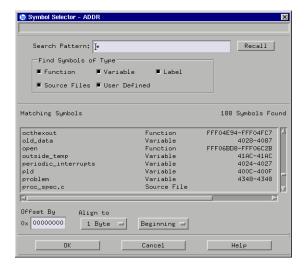

Object File Symbols 110

Requirements 110

To use object file symbols in the HP 16600A/700A 111

Compilers 112

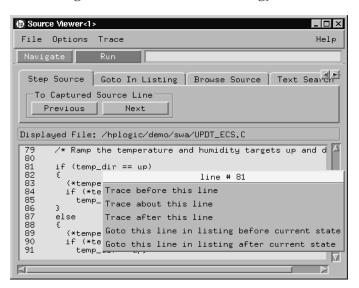

Source Code 116 Inverse Assembler Generated PC (Software Address) Label 118 Access to Source Code Files 119

Triggering on Symbols and Source Code 120

To avoid triggering on prefetched instructions 120

To correlate relocatable code using the address offset 121

#### 6 Connecting and Configuring the Emulation Module

Connecting and Configuring the Emulation Module 124

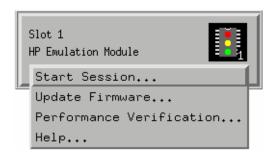

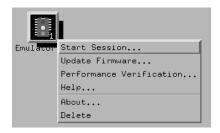

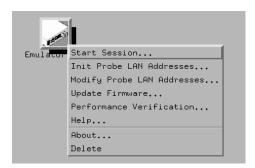

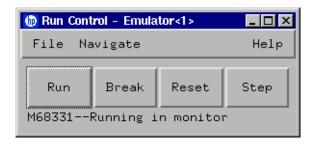

Using the Emulation Control Interface 125

To start the Emulation Control Interface from the main System window 127 To start the Emulation Control Interface from the Workspace window 127 To start the Emulation Control Interface from the Workspace window for an emulation probe 129

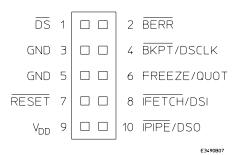

Designing a Target System for the Emulation Module 130 Debug port connections 130 8-pin BDM port 132 10-pin BDM port 132 Target  $V_{\rm DD-132}$  Enabling BDM 133

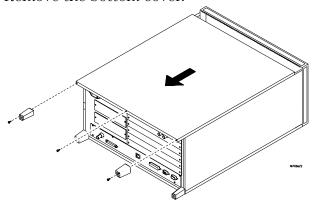

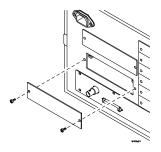

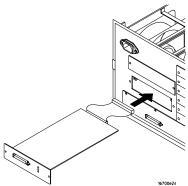

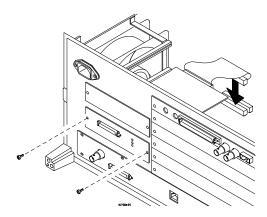

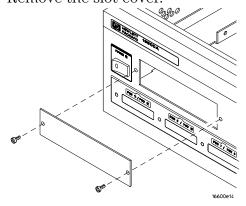

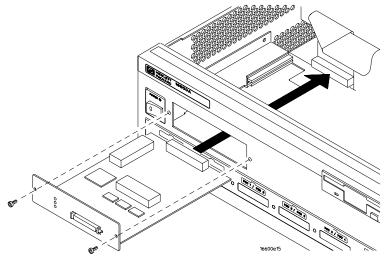

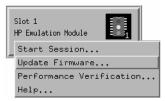

Installing the Emulation Module 134

To install the emulation module in an HP16700A-series logic analysis system or an HP16701A expansion frame  $\,$   $\,$  135  $\,$

To install the emulation module in an HP16600A-series logic analysis system  $\;\;$  137

To test the emulation module 138

Connecting the Emulation Module to the Target System 139

To connect to a target system using a 10-pin debug port  $\;$  140

To connect to a target system via an 8-pin debug port 141

To connect to a target system using an analysis probe 143

To update firmware 144

To display current firmware version information 145

To verify communication between the emulator and target system  $\,$  145

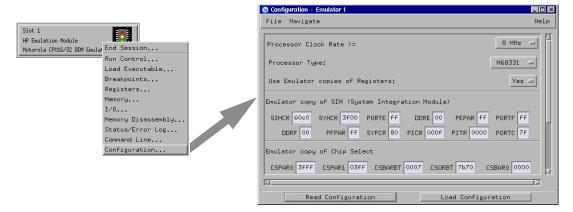

Configuring the Emulation Module 146

What can be configured 146

To configure using the Emulation Control Interface 147

To configure using the built-in commands 148

To configure using a debugger 149

To configure the processor type 150

To configure the processor clock speed (BDM communication speed) 151

To set the default clock rate if the processor clock rate is less than 8 MHz 152

Detailed information about processor clock rates 154

To configure restriction to real-time runs 156

Testing the emulator and target system 157

To test memory accesses 157

To test with a running program 157

#### 7 Using Internal Registers (SIM and EMSIM Registers)

Internal Registers (SIM and EMSIM Registers) 160

The purpose of SIM Registers 160

The purpose of EMSIM registers 160

Configuring the SIM Registers 161

Summary 161

How SIM Register Values are Set 161

The effect of processor type on the EMSIM registers 162

Using the Emulation Control Interface or built-in commands 162

Configuring EMSIM Register Values 163

To copy target SIM registers to EMSIM registers 163

To manually define EMSIM values 163

Configuring SIM Register Values 165

To copy EMSIM registers to target SIM registers 165

To manually define SIM values 166

Saving and Loading EMSIM Values 167

To save EMSIM values in a configuration file 167

To load EMSIM values from a configuration file 167

Configuring SIM and EMSIM Values Using Built-In Commands 169

To compare SIM and EMSIM registers 169

Summary of EMSIM-related built-in commands 170

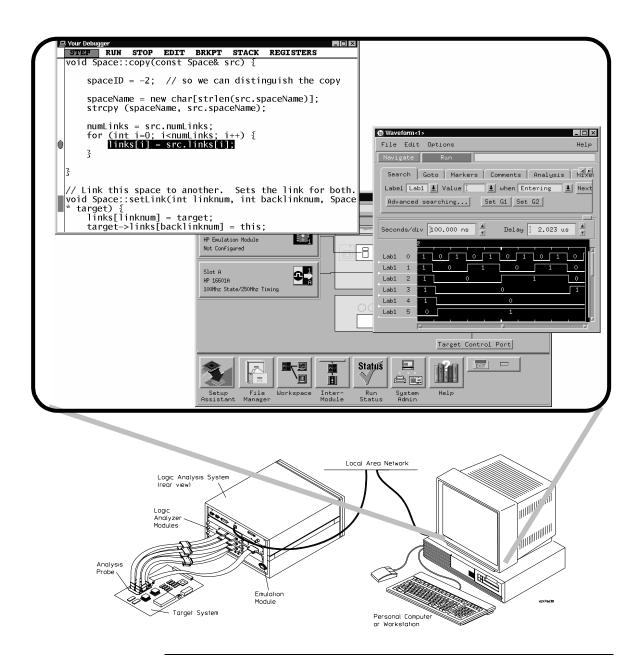

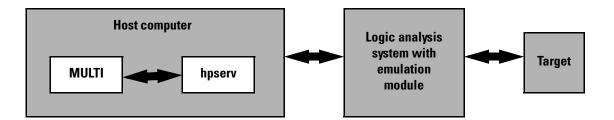

#### 8 Using the Emulator with a Debugger

Using the Emulator with a Debugger 174

Setting up Debugger Software 177

To connect the logic analysis system to the LAN 178

To change the port number of an emulator 180

To verify communication with the emulator 181

To export the logic analysis system's display to a workstation 182

To export the logic analysis system's display to a PC 183

Using the Green Hills debugger 184

Compatibility 184

Overview 184

Getting started 184

To configure the emulation module, analysis probe, and target using an initialization script 188

To perform common debugger tasks 190

To send commands to the emulation module 190

To view commands sent by MULTI to the emulation module 190

To reinitialize the system 191

To disconnect from the emulation module 191

Error conditions 191

Using the Software Development Systems debugger

Compatibility 193

Overview 193

Startup behavior 193

Getting started 194

To send commands to the emulation module 200

Download performance 201

Error conditions 202

#### 9 Using the Analysis Probe and Emulation Module Together

Using the Analysis Probe and Emulation Module Together 204 What are some of the tools I can use? 204

Which assembly-level listing should I use? 204

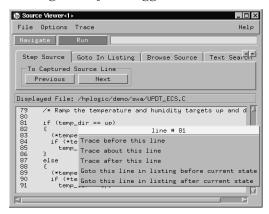

Which source-level listing should I use? 205

Where can I find practical examples of measurements? 205

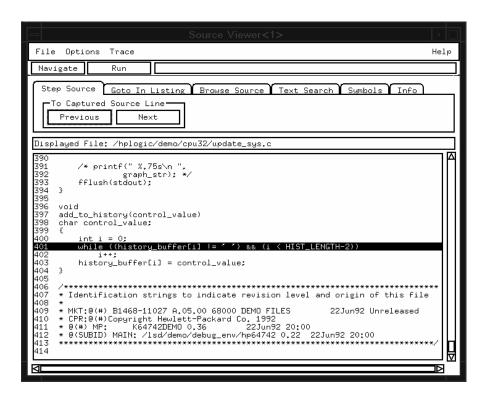

Triggering the Emulation Module from the Analyzer 206

To stop the processor when the logic analyzer triggers on a line of source code (Source Viewer window) 206

To stop the processor when the logic analyzer triggers (Intermodule window) 207

To minimize the "skid" effect 208

To stop the analyzer and view a measurement 208

Tracing until the processor halts 210

To capture a trace before the processor halts 210

Triggering the Logic Analyzer from the Emulation Module 211

The emulation module trigger signal 211

Group Run 212

To trigger the analyzer when the processor halts 214

To trigger the analyzer when the processor reaches a breakpoint 215

#### 10 Hardware Reference

Hardware Reference 218

Analysis probe—operating characteristics 219

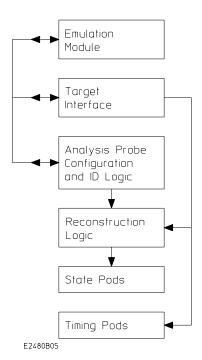

Theory of operation and clocking 220

Address reconstruction overview 220

Analysis probe signal-to-connector mapping (Timing) 223

State connector signal definition 231

Emulation module—operating characteristics 235

Emulation module—electrical characteristics 236

### 11 General-Purpose ASCII (GPA) Symbol File Format

General-Purpose ASCII (GPA) Symbol File Format 238

GPA Record Format Summary 240 SECTIONS 242 FUNCTIONS 243 VARIABLES 244 SOURCE LINES 245 START ADDRESS 246 Comments 246

#### 12 Troubleshooting the Analysis Probe

Troubleshooting the Analysis Probe 248

Logic Analyzer Problems 249

Intermittent data errors 249

Unwanted triggers 250

No activity on activity indicators 250

No trace list display 250

Analyzer won't power up 251

Analysis Probe Problems 252

Target system will not boot up 252

Erratic trace measurements 253

Capacitive loading 253

Inverse Assembler Problems 254

No inverse assembly or incorrect inverse assembly 254

Inverse assembler will not load or run 255

Intermodule Measurement Problems 256

An event wasn't captured by one of the modules 256

Analysis Probe Messages 257

"... Inverse Assembler Not Found" 257

"Measurement Initialization Error" 258

"No Configuration File Loaded" 259

"Selected File is Incompatible" 260

"Slow or Missing Clock" 260

"Time from Arm Greater Than 41.93 ms" 260

"Waiting for Trigger" 261

Returning Parts to Hewlett-Packard for Service 262

To return a part to Hewlett-Packard 262

To obtain replacement parts 263

Cleaning the Instrument 264

#### 13 Troubleshooting the Emulation Module

Solving Problems 266

Troubleshooting Guide 267

Emulation Module Status Lights 268

Emulation Module Built-in Commands 269

To telnet to the emulation module 269

To use the built-in commands 270

Problems with the BDM Connection 272 If a user interface behaves erratically 272

Problems with Configuration 273

If you have problems displaying some registers 273

If you have problems initializing some registers 273

Problems with the Target System 274

If boot area accesses fail 274

Problems with the LAN Interface 275

If LAN communication does not work 275

If it takes a long time to connect to the network 275

Problems with the Emulation Module 276

To run the built-in performance verification test using the logic analysis system  $\;\;276$

To run complete performance verification tests using a telnet connection 277 If a performance verification test fails 279

Returning Parts to Hewlett-Packard for Service 280 To return a part to Hewlett-Packard 280 To obtain replacement parts and cables 281

To clean the instrument 281

# Glossary

Overview

# Overview

This chapter describes:

- Setup Checklist

- Setup Assistant

- Equipment used with the analysis probe (including a list of logic analyzers supported)

- Equipment used with the emulation module

- System configurations

- Additional information sources

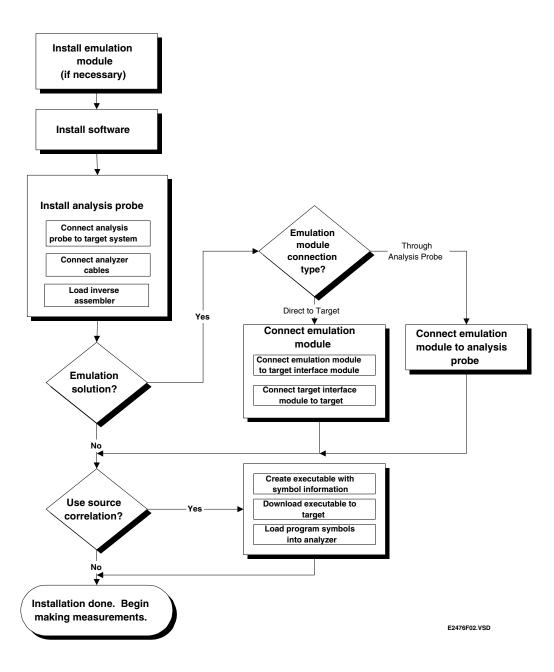

# Setup Checklist

Follow these steps to connect your equipment:

- Check that you received all of the necessary equipment. See page 20 (analysis probe) or page 25 (emulation module).

- If you need to install an emulation module in an HP 16600A/700A series logic analysis system, see page 134.

- Install the software. See page 29.

- If you have an HP 16600A/700A-series logic analysis system, use the Setup Assistant to help you connect and configure the analysis probe and emulation module. See page 19.

- If you do not have an HP 16600A/700A-series logic analysis system, install the analysis probe (see page 42).

#### **Setup Checklist**

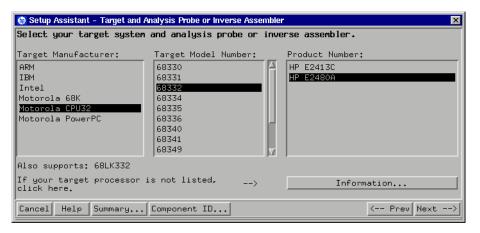

# Setup Assistant

The Setup Assistant is an online tool for connecting and configuring your logic analysis system for microcontroller and bus analysis. The Setup Assistant is available on the HP 16600A and HP 16700A-series logic analysis systems. You can use the Setup Assistant in place of the connection and configuration procedures provided in this manual.

This menu-driven tool will guide you through the connection procedures for connecting the logic analyzer to an analysis probe, an emulation module, or other supported equipment. It will also guide you through connecting an analysis probe to the target system.

Start the Setup Assistant by clicking its icon in the system window.

If you ordered this product with your HP 16600A/700A-series logic analysis system, the logic analysis system has the latest software installed, including support for this product. If you received this product after you received your logic analysis system, see the "Installing Software" chapter (page 29).

# Analysis Probe

This section lists equipment supplied with the analysis probe and equipment requirements for using the analysis probe.

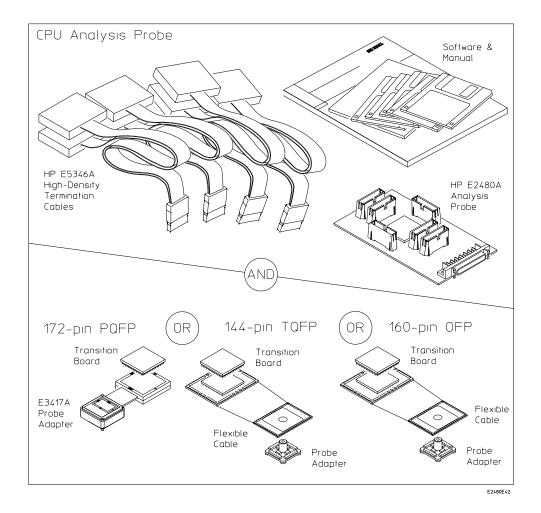

# Equipment supplied

The equipment supplied with the analysis probe is shown in the illustration on the next page. It is listed below:

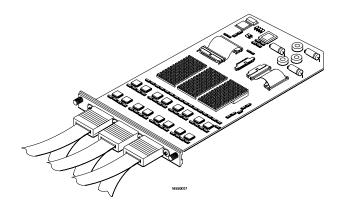

- The HP E2480A analysis probe circuit board.

- Four HP E5346A high-density termination cables.

- Logic analyzer configuration files and inverse assembler software on a CD-ROM (for HP 16600A/700A series logic analysis systems).

- Logic analyzer configuration files and inverse assembler software on five 3.5-inch disks (for other HP logic analyzers).

- This User's Guide.

- A package-specific probing kit (see below).

| Processor<br>Package  | 132-pin PQFP                | 144-pin TΩFP                | 160-pin QFP                 |

|-----------------------|-----------------------------|-----------------------------|-----------------------------|

|                       | 132-pin<br>Transition Board | 144-pin<br>Transition Board | 160-pin<br>Transition Board |

| Equipment<br>Supplied | E3417A<br>Probe Adapter     | E5336A<br>Probe Adapter     | E5373A<br>Probe Adapter     |

| Supplied              | User's Guide                | E5338A<br>Flexible Cable    | E5350A<br>Flexible Cable    |

|                       |                             | User's Guide                | User's Guide                |

**Equipment Supplied with the HP E2480A Analysis Probe**

# Minimum equipment required

For state and timing analysis of a Motorola CPU32 target system, you need all of the following items.

- The HP E2480A Analysis Probe.

- Four HP E5346A high-density cables.

- A microcontroller-specific transition board.

- A QFP probe adapter kit for your specific microcontroller package.

- The probe adapter User's Guide, for connecting the probe adapter to the target system.

- One of the logic analyzers listed on page page 23. The logic analyzer software version requirements are listed on page 24.

The above is the minimum equipment required to make a measurement. If you want to configure the analysis probe to reconstruct addresses, you must also have an emulation module.

# Additional equipment supported

**Emulation module.** The HP E2480A has a built-in connector for an emulation module.

**HP B4620B Source Correlation Tool Set.** The analysis probe and inverse assembler may be used with the HP B4620B Source Correlation Tool Set.

# Logic analyzers supported

The table below lists the logic analyzers supported by the HP E2480A analysis probe. Logic analyzer software version requirements are shown on the following page.

The HP E2480A requires four logic analyzer pods (68 channels) for inverse assembly. The analysis probe contains six high-density connectors (12 logic analyzer pods). Two of the connectors are for State analysis, and the other four are for Timing analysis.

#### **Logic Analyzers Supported**

| Logic Analyzer            | Channel<br>Count | State Speed | Timing Speed | Memory Depth        |

|---------------------------|------------------|-------------|--------------|---------------------|

| 16600A                    | 204              | 100 MHz     | 125 MHz      | 64 k states         |

| 16601A                    | 136              | 100 MHz     | 125 MHz      | 64 k states         |

| 16602A                    | 102              | 100 MHz     | 125 MHz      | 64 k states         |

| 16603A                    | 68               | 100 MHz     | 125 MHz      | 64 k states         |

| 16550A (one or two cards) | 102/card         | 100 MHz     | 250 MHz      | 4 k states          |

| 16554A (one or two cards) | 68/card          | 70 MHz      | 125 MHz      | 512 k states        |

| 16555A (one or two cards) | 68/card          | 110 MHz     | 250 MHz      | 1 M states          |

| 16555D (one or two cards) | 68/card          | 110 MHz     | 250 MHz      | 2 M states          |

| 16556A (one or two cards) | 68/card          | 100 MHz     | 200 MHz      | 1 M states          |

| 16556D (one or two cards) | 68/card          | 100 MHz     | 200 MHz      | 2 M states          |

| 16557D (one or two cards) | 68/card          | 135 MHz*    | 250 MHz      | 2 M states          |

| 1660A/AS/C/CS/CP          | 136              | 100 MHz     | 250 MHz      | 4 k states          |

| 1661A/AS/C/CS/CP          | 102              | 100 MHz     | 250 MHz      | 4 k states          |

| 1662A/AS/C/CS/CP          | 68               | 100 MHz     | 250 MHz      | 4 k states          |

| 1670A                     | 136              | 70 MHz      | 125 MHz      | 64 k or .5 M states |

| 1670D                     | 136              | 100 MHz     | 125 MHz      | 64 k or 1 M states  |

| 1671A                     | 102              | 70 MHz      | 125 MHz      | 64 k or .5 M        |

| 1671D                     | 102              | 100 MHz     | 125 MHz      | 64 k or 1 M         |

| 1672A                     | 68               | 70 MHz      | 125 MHz      | 64 k or .5 M        |

| 1672D                     | 68               | 100 MHz     | 125 MHz      | 64 k or 1 M         |

<sup>\*</sup>For the 16557D, the state and timing speeds decrease for four- or five-card configurations.

# Logic analyzer software version requirements

The logic analyzers must have software with a version number greater than or equal to those listed below to make a measurement with the HP E2480A. You can obtain the latest software at the following web site:

#### http://www.hp.com/go/logicanalyzer

If your software version is older than those listed, load new system software with the higher version numbers before loading the HP E2480A software.

#### **Logic Analyzer Software Version Requirements**

| Logic Analyzer            | Minimum Logic Analyzer Software Version for use with<br>HP E2480A                                |

|---------------------------|--------------------------------------------------------------------------------------------------|

| HP 16600A-<br>series      | The latest HP 16600A logic analyzer software version is on the CD-ROM shipped with this product. |

| HP 1660A/AS<br>Series     | 3.01                                                                                             |

| HP 1660C/CS/<br>CP Series | A.02.01                                                                                          |

| HP 1670A/D<br>Series      | A.02.02                                                                                          |

| Mainframes*               |                                                                                                  |

| HP 16700A-                | The latest HP 16700A logic analyzer software version is on the CD-                               |

| series                    | ROM shipped with this product.                                                                   |

| HP 16500C                 | 1.07                                                                                             |

| Mainframe                 |                                                                                                  |

| HP 16500B<br>Mainframe    | 3.14                                                                                             |

<sup>\*</sup> The mainframes are used with the HP 16550 and HP 16554/55/56 logic analyzers.

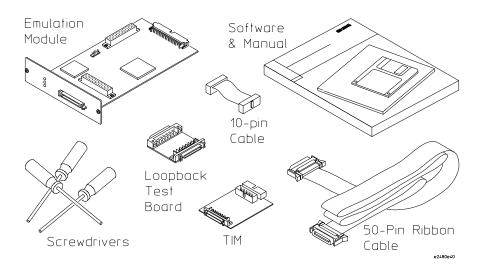

## **Emulation Module**

This section lists equipment supplied with the emulation module and lists the minimum equipment required to use the emulation module.

# Equipment supplied

The equipment supplied with your emulation module includes:

- An HP 16610A emulation module. If you ordered an emulation module as part of your HP 16600A or HP 16700A logic analysis system, it is already installed in the frame.

- A target interface module (TIM) circuit board.

- A emulation module loopback test board (HP part number E3496-66502).

- Firmware for the emulation module and/or updated software for the Emulation Control Interface on a CD-ROM.

- A 50-pin ribbon cable for connecting the emulation module to the target interface module or the HP E2480A analysis probe.

- A 10-pin ribbon cable for connecting the target interface module to the target system.

- Torx T-8, T-10 and T-15 screwdrivers.

- This User's Guide.

**Equipment Supplied with the Emulation Module**

# Minimum equipment required

The following equipment is required to use the emulation module:

A method for connecting to the target system. The HP E2480A analysis probe provides a debug port connector. You can also design a debug port connector on the target system (see "Designing a Target System for the Emulation Module" on page 130).

- An HP 16600A or HP 16700A logic analysis system.

- A user interface, such as a high-level source debugger or the logic analysis system's Emulation Control Interface.

## **Emulation Solution**

An emulation solution uses the equipment and software already described in this chapter.

The combination of an analysis probe, an emulation module, and an HP 16600A or HP 16700A logic analysis system lets you both trace and control microcontroller activity on the target system.

The analysis probe supplies signals from the target microcontroller to the logic analyzer. A configuration file sets up the logic analyzer to properly interpret these signals.

You can use a debugger or the logic analysis system's Emulation Control Interface to configure and control the target processor and to download program code. You can use the HP B4620B Source Correlation Tool Set to analyze high-level source code using the logic analysis system.

## Additional Information Sources

Additional or updated information can be found in the following places:

Newer editions of this manual may be available. Contact your local HP representative.

If you have a probing adapter, the instructions for connecting the probe to your target microcontroller are in the **Probing Adapter** documentation.

Application notes may be available from your local HP representative or on the World Wide Web at:

#### http://www.hp.com/go/logicanalyzer

If you have an HP 16600A or HP 16700A logic analysis system, the **online help** for the Emulation Control Interface has additional information on using the emulation module.

The **measurement examples** include valuable tips for making emulation and analysis measurements. You can find the measurement examples under the system help in your HP 16600A/700A logic analysis system.

If you cannot easily find the information you need, send email to documentation@col.hp.com. Your comments will help HP improve future manuals. (This address is for comments only; contact your local HP representative if you need technical support.)

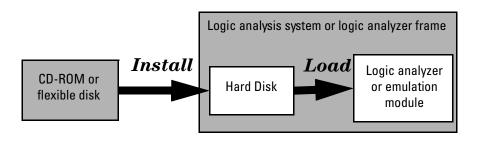

**Installing Software**

# **Installing Software**

This chapter explains how to install the software you will need for your analysis probe or emulation solution.

# Installing and loading

**Installing** the software will copy the files to the hard disk of your logic anlysis system. Later, you will need to **load** some of the files into the appropriate hardware module.

#### What needs to be installed

#### HP 16600A/700A-series logic analysis systems

If you ordered an emulation solution with your logic analysis system, the software was installed at the factory.

The following files are installed when you install a processor support package from the CD-ROM:

- Logic analysis system configuration files

- Inverse assembler (automatically loaded with the configuration files)

- Personality files for the Setup Assistant

- Emulation module firmware (for emulation solutions)

- Emulation Control Interface (for emulation solutions)

The HP B4620B Source Correlation Tool Set is installed with the logic analysis system's operating system.

# Other HP logic analyzers

The following files can be installed from a floppy disk:

• Logic analyzer configuration files, which automatically load the inverse assembler

# To install the software from CD-ROM (HP 16600A/700A)

Installing a processor support package from a CD-ROM will take just a few minutes. If the processor support package requires an update to the HP 16600A/700A operating system, installation may take approximately 15 minutes.

If the CD-ROM drive is not connected, see the instructions printed on the CD-ROM package.

- 1 Turn on the CD-ROM drive first and then turn on the logic analysis system.

- **2** Insert the CD-ROM in the drive.

- **3** Click the **System Admin** icon.

- 4 Click Install....

Change the media type to "CD-ROM" if necessary.

- 5 Click Apply.

- **6** From the list of types of packages, select "PROC-SUPPORT." A list of the available processor support packages will be displayed.

- 7 Click on the "M683XX" package.

If you are unsure if this is the correct package, click Details for information on what the package contains.

8 Click Install....

The dialog box will display "Progress: completed successfully" when the installation is complete.

9 Click Close.

The configuration files are stored in /hplogic/configs/hp/processor. The inverse assemblers are stored in /hplogic/ia.

#### See Also

The instructions printed on the CD-ROM package for a summary of the installation instructions.

The online help for more information on installing, licensing, and removing software.

# To list software packages which are installed (HP 16600A/700A)

In the System Administration Tools window, click **List...** .

# To install software on other logic analyzers

Consult the documentation for your logic analyzer for details.

Connecting and Configuring the Analysis Probe

# Connecting and Configuring the Analysis Probe

This chapter shows you how to connect the logic analyzer to the target system through the analysis probe.

If you are connecting to an HP 16600A-series or HP 16700A-series logic analyzer, use the Setup Assistant to connect and configure your system (see page 19). Use this manual for additional information, if desired.

If you are not using the Setup Assistant, follow the instructions given in this chapter. This chapter covers the following tasks; the order shown here is the recommended order for performing these tasks:

- Check that the target system meets the necessary requirements

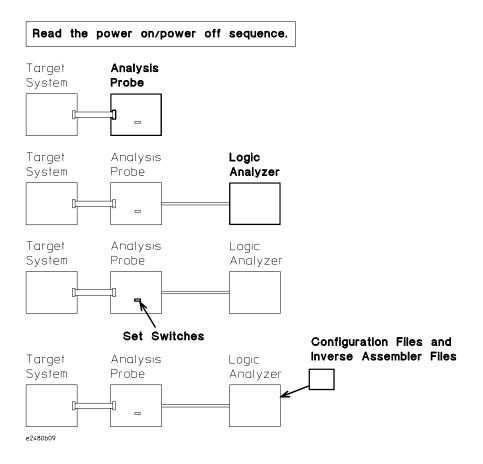

- Read the power on/power off sequence

- Connect the analysis probe to the target system

- Connect the analysis probe to the logic analyzer

- Configure the logic analyzer

## **Target System Requirements**

The HP E2480A connects to a number of microcontrollers and packages. The keep-out area and clearance requirements are described below.

### Keep-out area on the target board

The keep-out area varies according to which probe adapter you are using. Refer to the documentation included with your probe adapter for keep-out area and dimensions.

### Clearance above the target board

See the diagram on the next page for the dimensions of the analysis probe. You must also allow space for the cables which plug into the top of the analysis probe.

See Also

The data sheet for your analysis probe, available from your HP representative, has more detailed information and diagrams regarding the keep-out area and analysis probe dimensions.

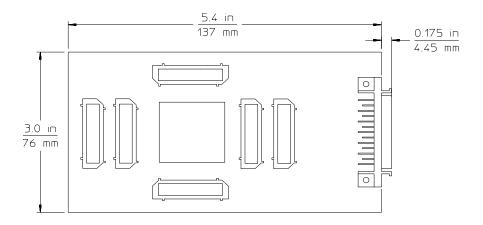

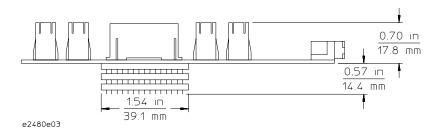

## Analysis probe—circuit board dimensions

The following figure gives the dimensions for the analysis probe circuit board. The dimensions are listed in inches and millimeters.

**Analysis Probe Circuit Board Dimension Diagram**

# Power-on/Power-off Sequence

Listed below are the sequences for powering on and off a fully connected system. Simply stated, your target system is always the last to be powered on, and the first to be powered off.

# To power on HP 16600A and HP 16700A-series logic analysis systems

Ensure the target system is powered off.

- 1 Turn on the logic analyzer. The Setup Assistant will guide you through the process of connecting and configuring the analysis probe.

- **2** When the analysis probe is connected to the target system and logic analyzer, and everything is configured, turn on your target system.

## To power on all other logic analyzers

With all components connected, power on your system in the following order:

- Logic analysis system.

- Your target system.

# To power off

- Turn off your target system.

- Turn off your logic analysis system.

#### **Connection Sequence**

# Connecting the Analysis Probe to the Target System

This section explains how to connect the HP E2480A analysis probe to the target system. Connecting the analysis probe to the target system consists of the following steps.

Note that there are separate instructions for the different QFP packages. The instructions in this manual are only an overview. Use the documentation included with your probe adapter for detailed connecting procedures.

- Turn off the target system.

- Turn off the logic analyzer (unless you are using an HP 16600/16700A logic analysis system).

- Connect the transition board to the analysis probe.

- Connect analysis probe/transition board to the probe adapter.

- Connect the probe adapter to the target system.

The remainder of this section describes these general steps in more detail.

### **Protect Your Equipment**

The analysis probe socket assembly pins are covered for shipment with a conductive foam wafer or conductive plastic pin protector. This is done to protect the delicate gold-plated pins from damage due to impact. When you're not using the analysis probe, protect the socket assembly pins from damage by covering them with the pin protector.

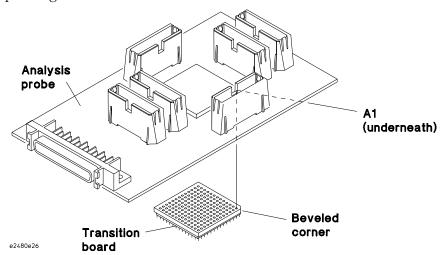

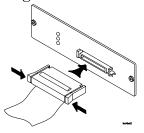

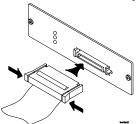

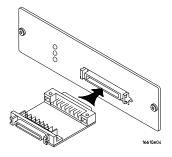

#### To connect the transition board

The microcontroller-specific transition board properly routes the signals from the probe adapter to the analysis probe. To connect the transition board to the analysis probe:

- Verify that there are no bent pins on the PGA socket of the analysis probe.

- Align the beveled corner of the transition board with the pin A1 corner of the PGA connector on the underside of the analysis probe. The illustration below shows the beveled corner and the pin A1 corner, as seen from the top of the analysis probe.

#### **CAUTION:**

Serious damage to the target system or analysis probe can result from incorrect connection. Note the position of pin 1 (or pin A1) on the target system, transition board, and the analysis probe prior to making any connection. Also, take care to align the analysis probe connector with the pins on the probe adapter assembly so that all pins are making contact.

Once all pins are aligned correctly, firmly press the transition board onto the analysis probe PGA socket. You might need a solid surface to press against.

Pin A1 Corner and Transition Board Alignment

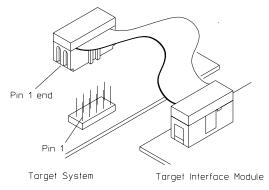

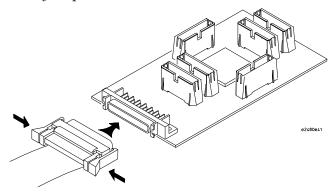

# To connect the analysis probe to the probe adapter

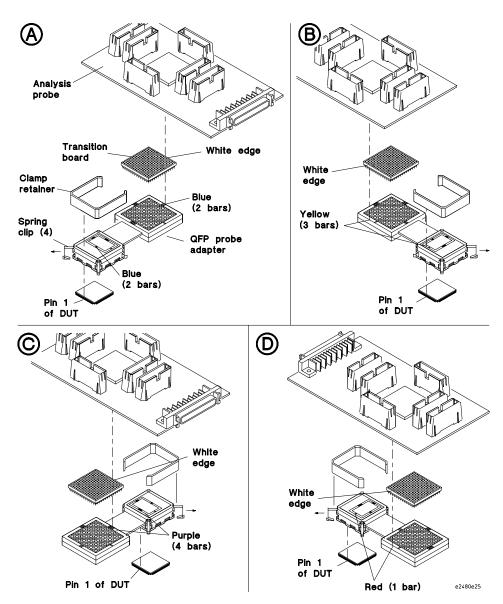

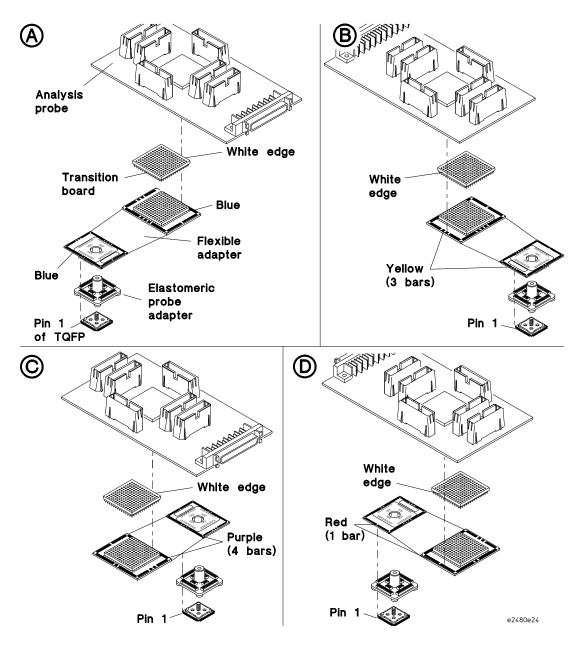

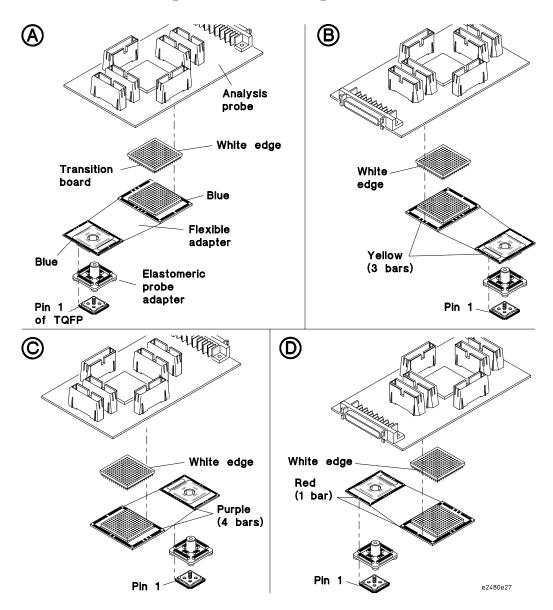

The orientation of the analysis probe with respect to the probe adapter depends on the orientation of the probe adapter with respect to pin 1 of the target system. Use the appropriate illustration from the following pages to ensure you have the proper orientation. To connect the analysis probe to the probe adapter:

Verify that there are no bent pins on the PGA socket of the transition board.

Note the color (or number of black squares) on the side of the probe adapter or flexible cable that is connected to the pin 1 side of the target system microcontroller. Orient the analysis probe so that the solid white side of the transition board aligns with the same color (or number of black squares) on the PGA end of the probe adapter or flexible cable.

#### **CAUTION:**

Serious damage to the target system or analysis probe can result from incorrect connection. Note the position of pin 1 (or pin A1) on the target system, transition board, and the analysis probe prior to making any connection. Also, take care to align the analysis probe connector with the pins on the probe adapter assembly so that all pins are making contact.

Once all pins are aligned correctly, firmly press the analysis probe/ transition board onto the PGA socket of the probe adapter or flexible cable.

# Connecting the probe adapter to the target system

The microcontrollers supported by the HP E2480A analysis probe come in a variety of QFP packages. The QFP probe adapter assemblies allow the analysis probe to be connected to the target system without removing the microcontroller from the target system. Refer to the documentation for your probe adapter for information on attaching the QFP Probe Adapter to your target system.

The illustrations on the following pages show the allowable rotations for the different QFP probe adapters when used with the HP E2480A. Note that the orientation (rotation) of the analysis probe with respect to the probe adapter depends on the orientation (rotation) of the probe adapter with respect to the target system. To ensure that you do not have mechanical interference between the analysis probe and the target system, use the rotation diagrams on the following pages, and the instructions in "To connect the analysis probe to the probe adapter," to determine the desired orientation before you connect the probe adapter to the target system.

#### **CAUTION:**

Serious damage to the target system or analysis probe can result from incorrect connection. Note the position of pin 1 (or pin A1) on the target system, transition board, and the analysis probe prior to making any connection. Also, take care to align the analysis probe connector with the pins on the probe adapter assembly so that all pins are making contact.

#### **CAUTION:**

To prevent equipment damage, remove power from all system components before making attachments.

### 132-pin PQFP Probe Adapter Rotations

132-Pin PQFP Probe Adapter Rotation Diagram

### 144-pin TQFP Probe Adapter Rotations

144-Pin TQFP Probing System Rotation Diagram

### 160-pin QFP Probe Adapter Rotations

160-Pin QFP Probing System Rotation Diagram

# Connecting the Analysis Probe to the Logic Analyzer

This section shows the connections between the logic analyzer pod cables and the high-density cables on the analysis probe. Use the appropriate page for your logic analyzer. The configuration file names for each logic analyzer are included with the connection diagrams.

**Number of Pods Used/Required.** The type of measurement to be made determines the number of logic analyzer pods to be used. State measurements require four pods. Full timing measurements require eight pods. If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

This section shows diagrams for connecting the analysis probe to the logic analyzers listed below:

- HP 16600A logic analyzers (page 52)

- HP 16601A logic analyzers (page 54)

- HP 16602A logic analyzers (page 56)

- HP 16603A logic analyzers (page 58)

- HP 16550A logic analyzers (one or two cards) (page 60)

- HP 16554/55/56/57 logic analyzers (one or two cards) (page 63)

- HP 1660A/AS/C/CS/CP (page 65)

- HP 1661A/AS/C/CS/CP logic analyzers (page 67)

- HP 1662A/AS/C/CS/CP logic analyzers (page 69)

- HP 1670A/D logic analyzers (page 71)

- HP 1671A/D logic analyzers (page 73)

- HP 1672A/D logic analyzers (page 75)

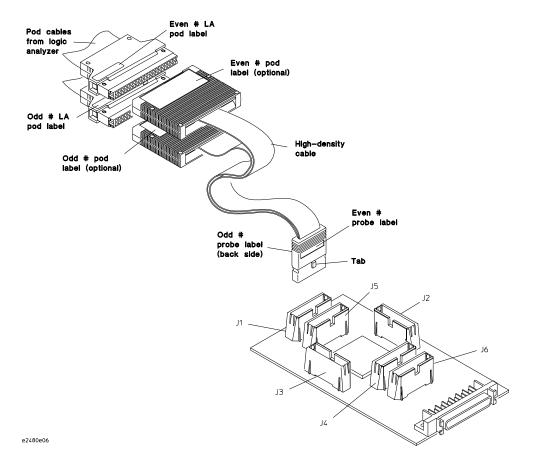

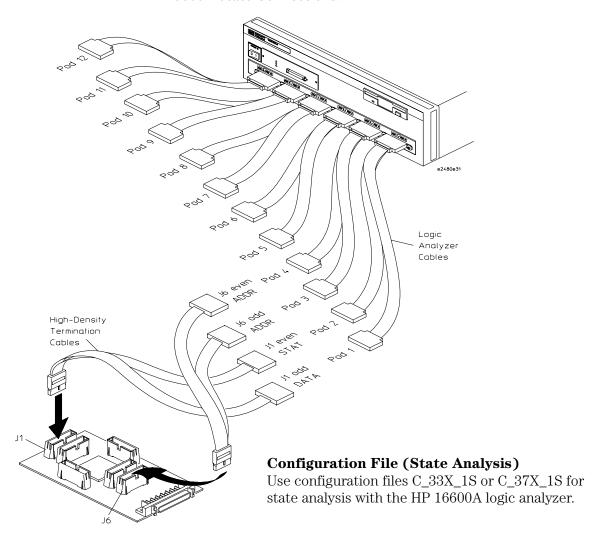

# To connect the high-density termination cables to the analysis probe

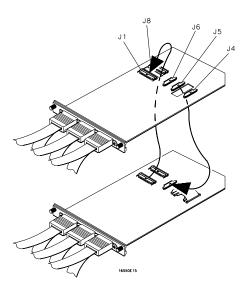

Four HP E5346A high-density termination cables, and labels to identify them, are included with the HP E2480A. Connect the cables to the connectors on the analysis probe as shown in the illustration below. Attach the labels to the cables after connecting the cables to the logic analyzer. Note that J1 and J6 are State connectors, and J2 through J5 are Timing connectors.

**Connecting High-Density Cables to the Analysis Probe**

# Connecting the high-density cables to the logic analyzer

The following pages show the connections between the logic analyzer pod cables and the high-density cables of the analysis probe. Note that for each logic analyzer, there are separate connections for State and Timing. Refer to the appropriate pages for your logic analyzer. The configuration file names for each logic analyzer and each CPU32 target system are included with the connection diagrams.

**Analysis Probe Pod Locations**

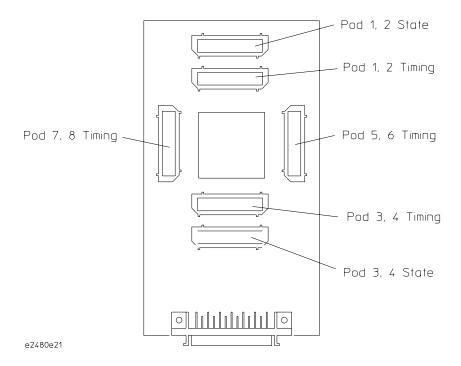

## To connect to the HP 16600A logic analyzer

Use the following figures to connect the analysis probe to the HP 16600A logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 16600A State Connections.

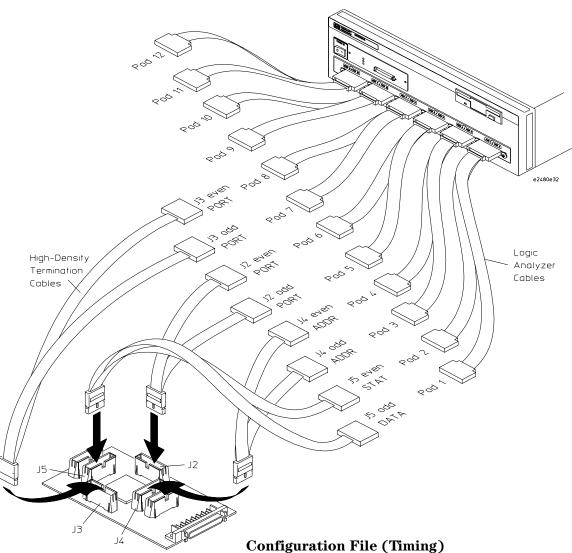

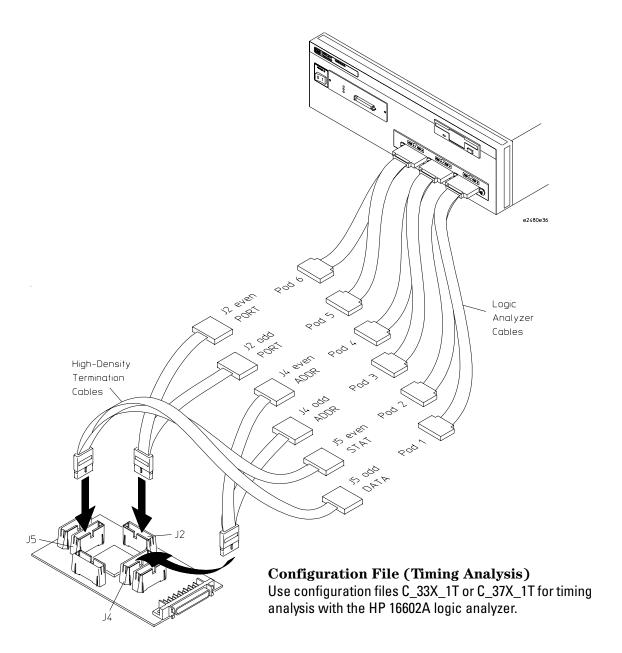

### **HP 16600A Timing Connections.**

Use configuration file C\_33X\_1T or C\_37X\_1T for Timing analysis with the HP 16600A logic analyzer.

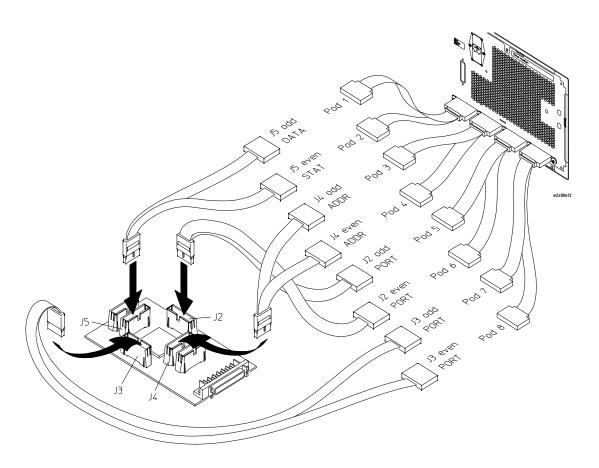

## To connect to the HP 16601A logic analyzer

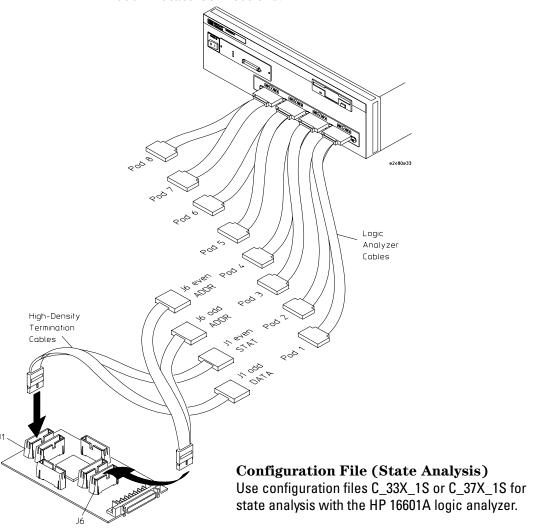

Use the following figures to connect the analysis probe to the HP 16601A logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 16601A State Connections.

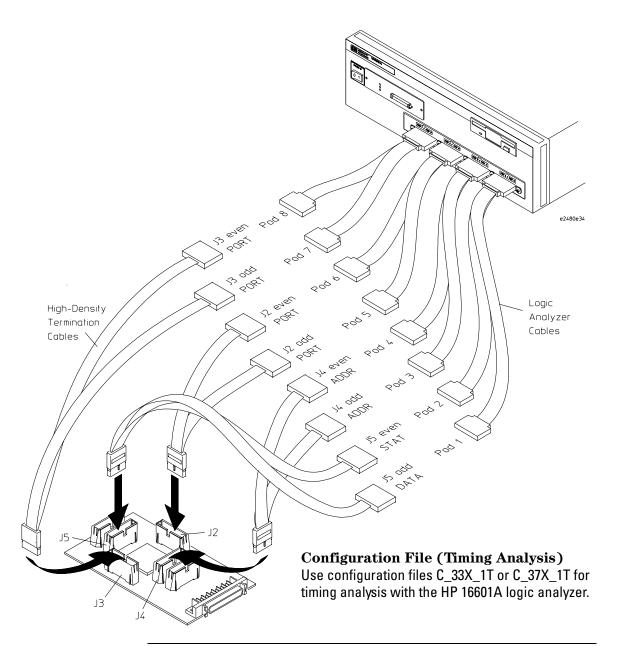

### **HP 16601A Timing Connections**

### To connect to the HP 16602A logic analyzer

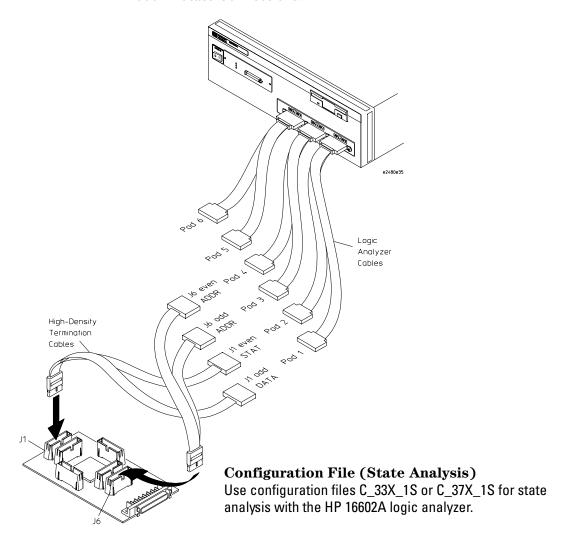

Use the following figures to connect the analysis probe to the HP 16602A logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 16602A State Connections.

### **HP 16602A Timing Connections.**

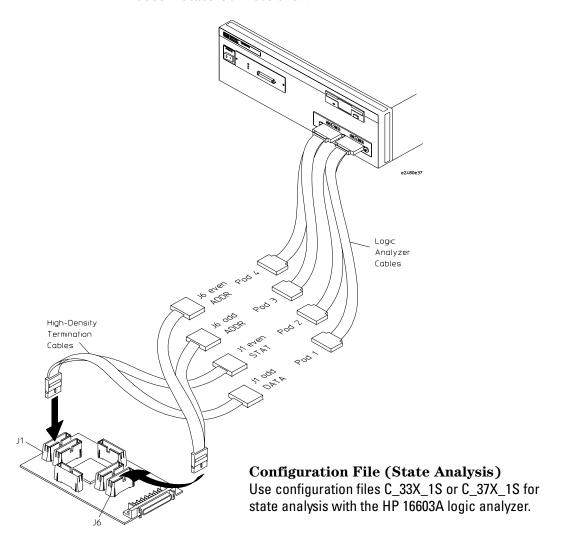

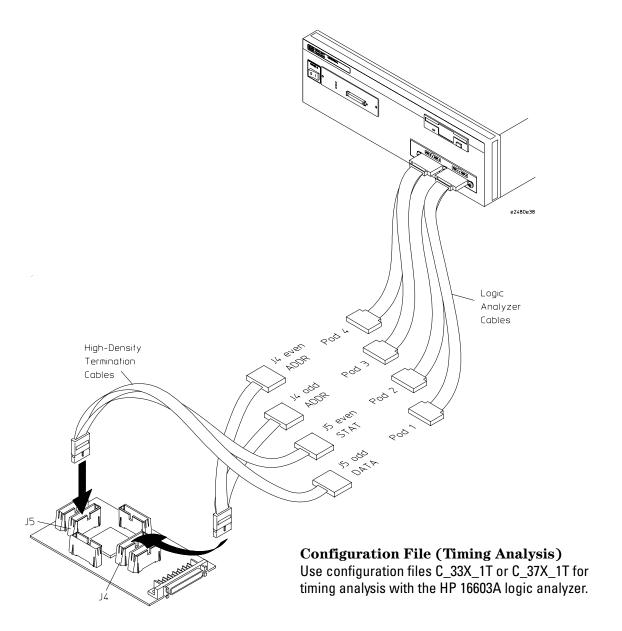

### To connect to the HP 16603A logic analyzer

Use the following figures to connect the analysis probe to the HP 16603A logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections

#### HP 16603A State Connections. .

### **HP 16603A Timing Connections.**

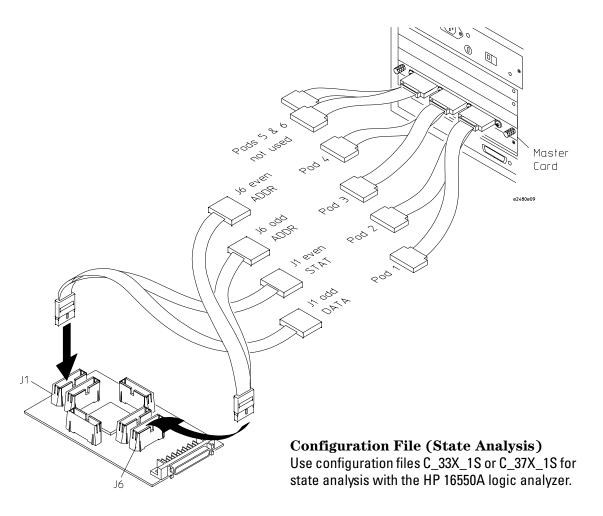

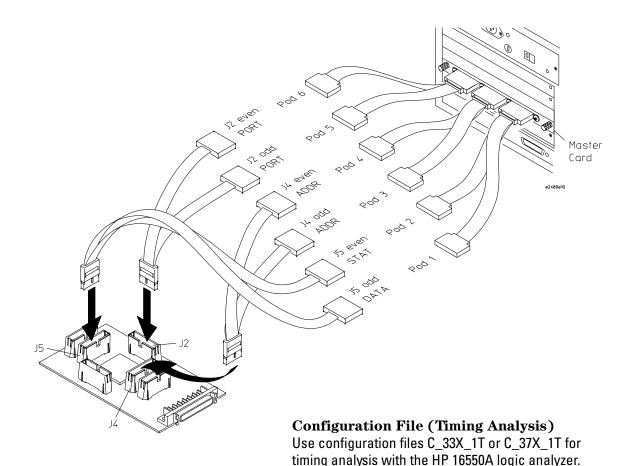

## To connect to the HP 16550A analyzer

Use the following figures to connect the analysis probe to the HP 16550A logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 16550A State Connections.

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

#### One-card HP 16550A Timing Connections.

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

### Two-card HP 16550A Timing Connections.

# Configuration File (Timing Analysis) Use configuration files C\_33X\_1T or C\_37X\_1T for timing analysis with the HP 16550A logic analyzer.

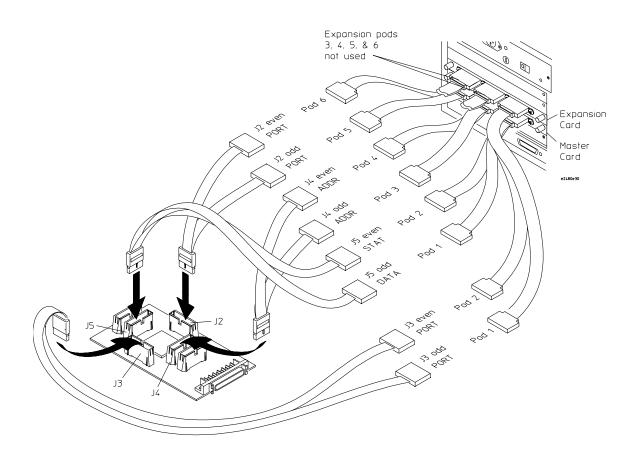

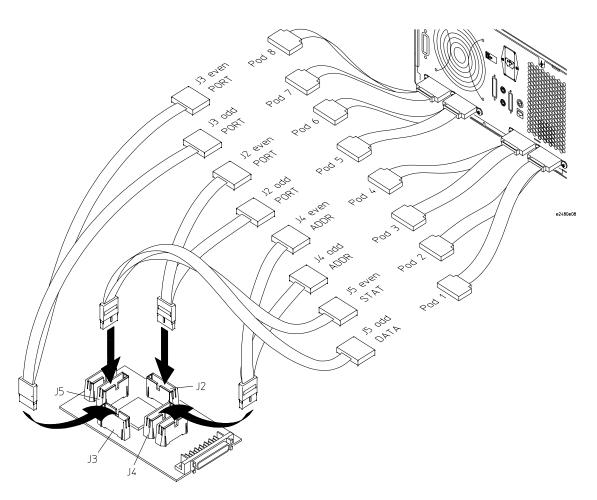

# To connect to the HP 16554/55A/56/57D analyzers

Use the following figures to connect the analysis probe to the HP 16554A/55A/56A and HP 16555D/56D/57D logic analyzers. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 16554/55/56/57 State Connections.

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

#### One- or two-card HP 16554/55/56/57 Timing Connections.

## **Configuration File (Timing Analysis)**

Use configuration files C\_33X\_2T or C\_37X\_2T for timing analysis with the HP 16554/55/56/57 logic analyzers.

# To connect to the HP 1660A/AS/C/CS/CP logic analyzers

Use the following figures to connect the analysis probe to the HP 1660A/C logic analyzers. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

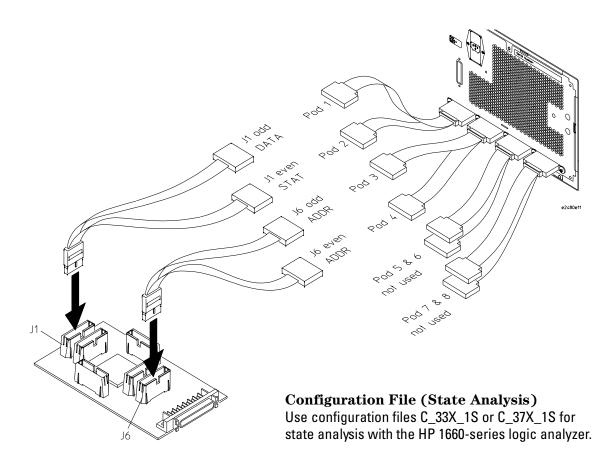

#### HP 1660-series State Connections. .

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

### **HP 1660-series Timing Connections.**

## **Configuration File (Timing Analysis)**

Use configuration files C\_33X\_1T or C\_37X\_1T for timing analysis with the HP 1660-series logic analyzer.

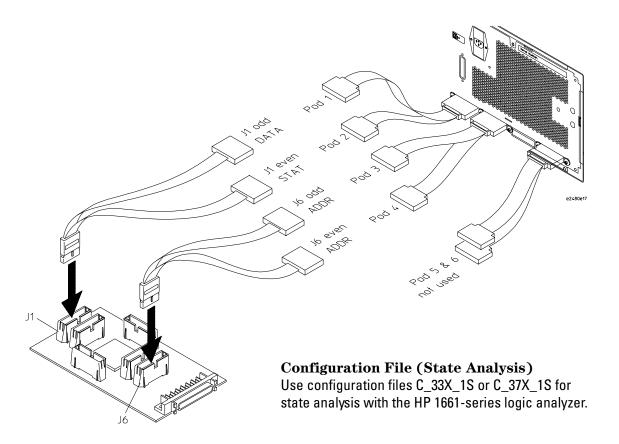

# To connect to the HP 1661A/AS/C/CS/CP logic analyzers

Use the following figures to connect the analysis probe to the HP 1661A/C logic analyzers. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 1661-series State Connections. .

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

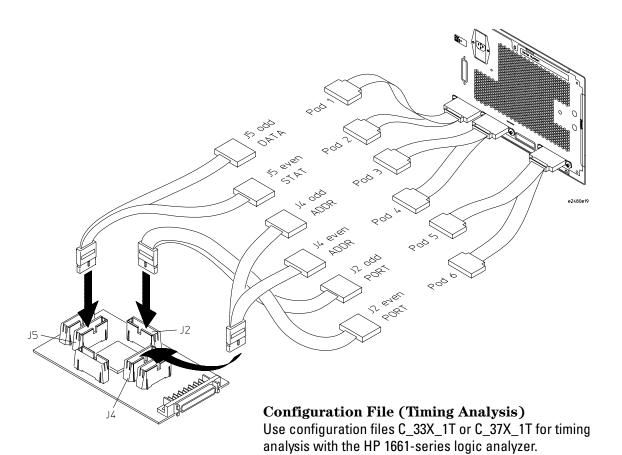

#### **HP 1661-series Timing Connections.**

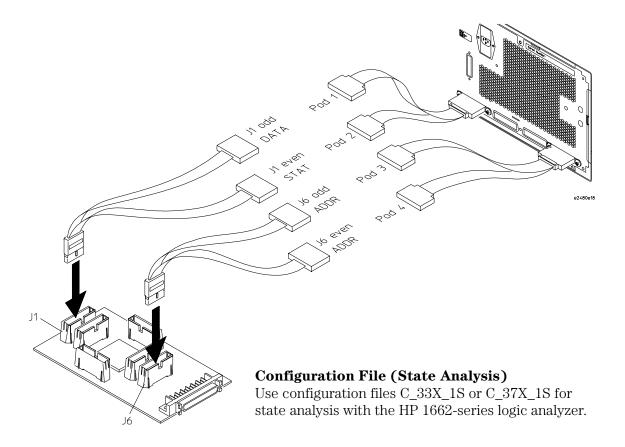

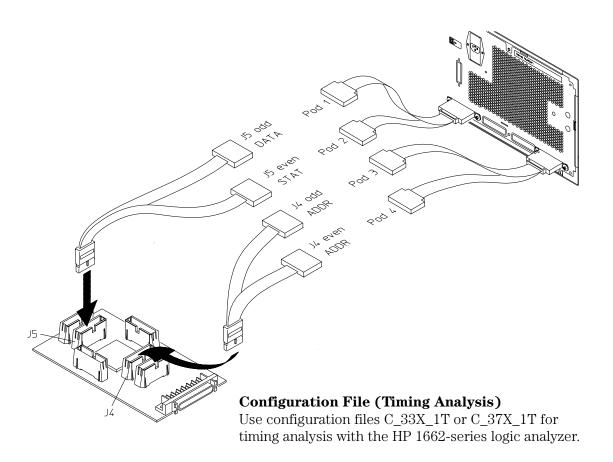

# To connect to the HP 1662A/AS/C/CS/CP logic analyzers

Use the following figures to connect the analysis probe to the HP 1662A/C logic analyzers. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 1662-series State Connections. .

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

#### **HP 1662-series Timing Connections.**

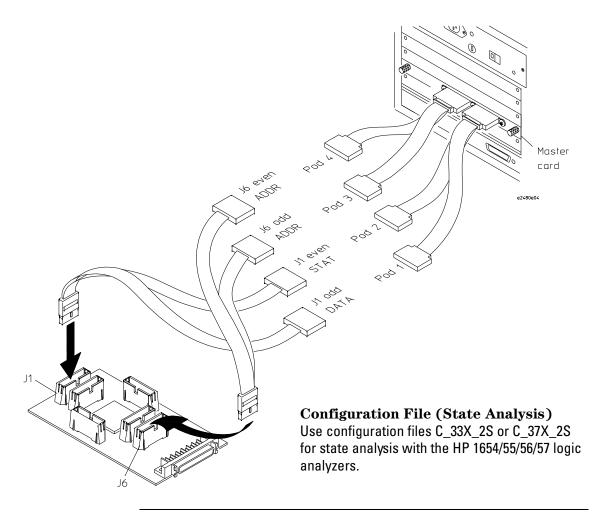

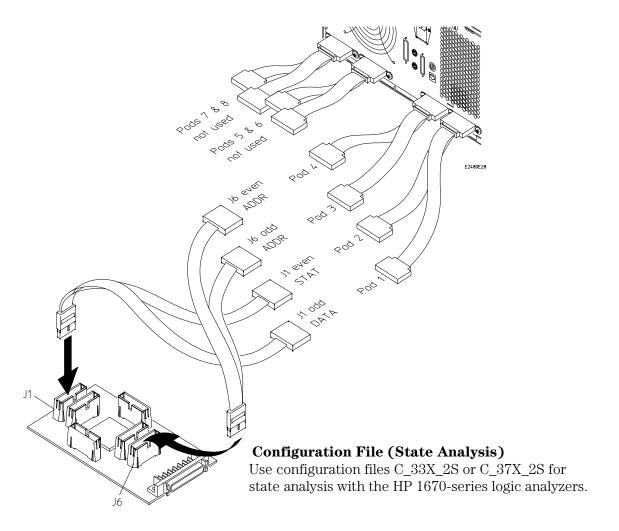

## To connect to the HP 1670A/D logic analyzer

Use the following figures to connect the analysis probe to the HP 1670A/D logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 1670-series State Connections. .

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

### **HP 1670-series Timing Connections.**

### **Configuration File (Timing Analysis)**

Use configuration files C\_33X\_2T or C\_37X\_2T for timing analysis with the HP 1670-series logic analyzer.

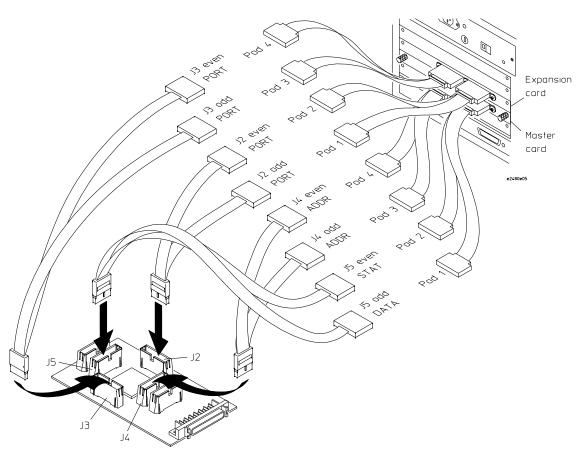

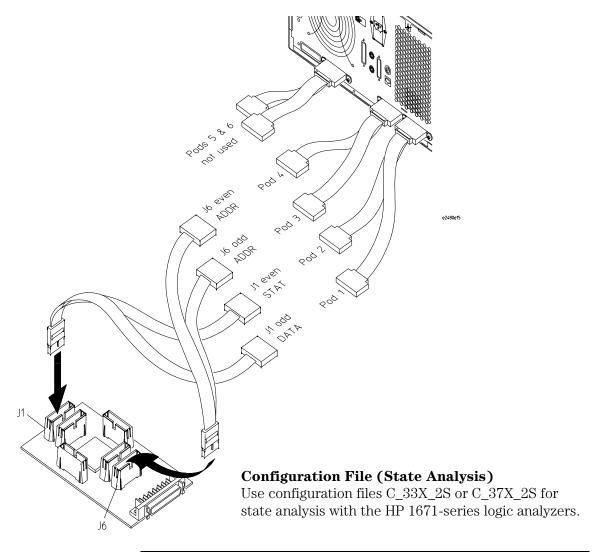

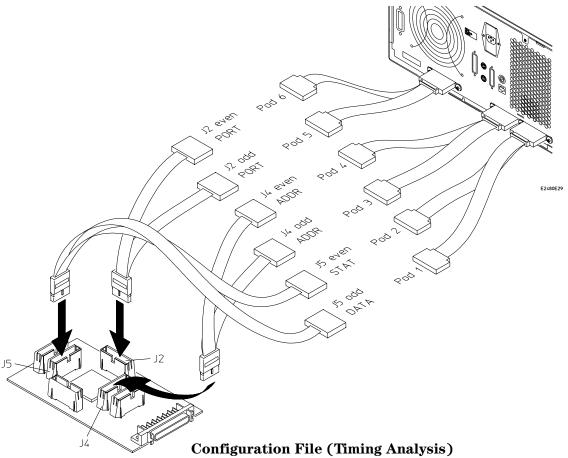

## To connect to the HP 1671A/D logic analyzer

Use the following figures to connect the analysis probe to the HP 1671A/D logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 1671-series State Connections. .

## Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

#### **HP 1671-series Timing Connections.**

Use configuration files C\_33X\_2T or C\_37X\_2T for timing analysis with the HP 1671-series logic analyzer.

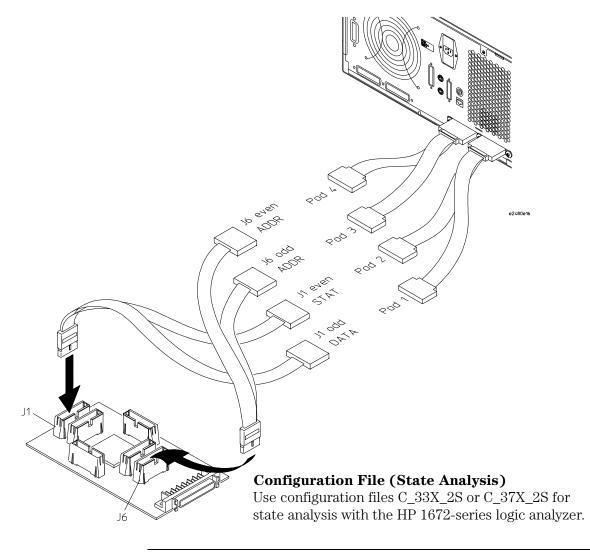

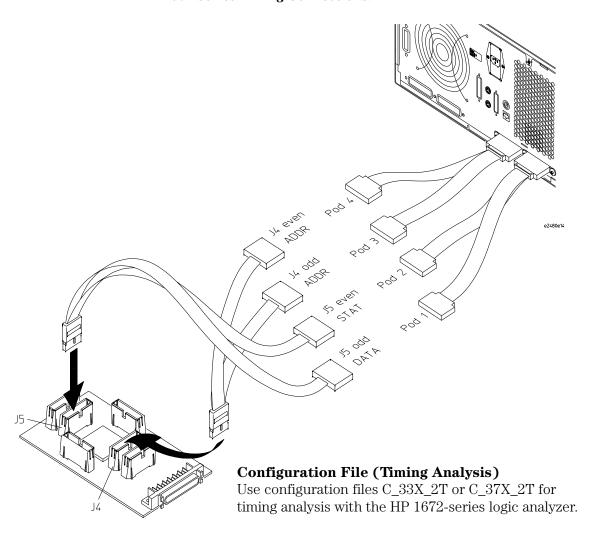

## To connect to the HP 1672A/D logic analyzer

Use the following figures to connect the analysis probe to the HP 1672A/D logic analyzer. Find the labels that were shipped with the high-density cables and use them to help identify the connections.

#### HP 1672-series State Connections. .

# Chapter 3: Connecting and Configuring the Analysis Probe Connecting the Analysis Probe to the Logic Analyzer

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, viewing the logic analyzer FORMAT menu shows the pod allocations. If the allocations will not acquire the desired signals, the allocations can be altered manually.

#### **HP 1672-series Timing Connections.**

## Configuring the Analysis Probe

Configuring the analysis probe consists of the following:

- Setting the ID switches

- Interpreting the LEDs

- Configuring the analysis probe for address reconstruction

The functionality of the analysis probe and logic analyzer, and the accuracy of displays provided by the inverse assembler, depend on the address-reconstruction feature of the analysis probe.

#### See Also

"Address reconstruction overview" on page 220 for a description of address reconstruction and its relationship to logic analyzer functionality.

#### To set the ID switches

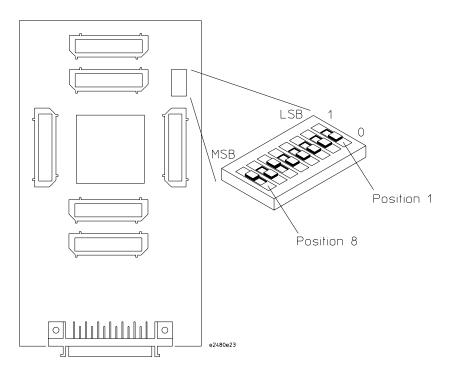

The HP E2480A provides an identification (ID) which may be used by other system components. The ID consists of primary and secondary values. The primary value is fixed (identifies CPU32 family) by hardware. The secondary ID is set by the 8-bit switch on the analysis probe, which must be configured to match the microcontroller being used. Positions 1 - 7 of the switch generate a binary value which must correspond to the last two digits of the microcontroller (binary 32 for MC68332). Position 8 is reserved and should be set to the "1" position.

The figure below shows the switch settings for the MC68332.

**Switch Settings for MC68332 Target System**

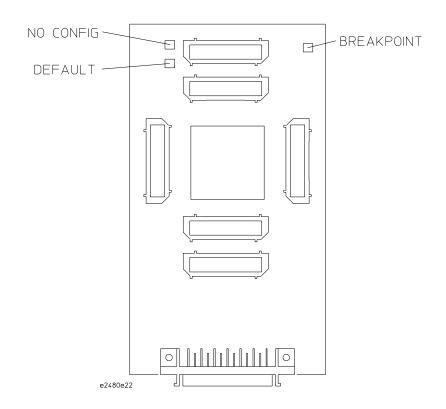

## To interpret the LEDs

The LEDs on the analysis probe hardware have meanings described below, after the following has been done:

- 1. The ID switches have been set (described in previous section).

- 2. The analysis probe configuration has been downloaded.

#### **LED Interpretations**

LED DS1 - Default

This LED identifies the type of configuration loaded into the reconstruction hardware. If the LED is lit, the default configuration is loaded. If this LED is not lit, a custom configuration is loaded. This LED only has meaning if LED DS2 is not lit.

LED DS2 - NO CONFIG

This LED indicates whether or not a configuration has been loaded into the analysis probe. If it is lit, no configuration has been loaded. If it is not lit, a configuration has been loaded.

• LED DS3 - Reserved for future support of hardware breakpoints.

The illustration on the following page shows the HP E2480A LEDs.

If DS2 remains lit after power has been applied to the analysis probe, the analysis probe contains an unknown reconstruction configuration. To resolve this unknown state, cycle power to the analysis probe or execute a "pp load" command (see next section).

Chapter 3: Connecting and Configuring the Analysis Probe Configuring the Analysis Probe

#### **HP E2480A LED Locations**

# Configuring the analysis probe for address reconstruction

The HP E2480A is shipped with all reconstruction disabled. This analysis probe configuration provides accurate analysis when A[19:23], FC[0:2], SIZ0, SIZ1, DSACK0, and DSACK1 are valid. If your target system is configured differently, you must configure the analysis probe to match your target system configuration.

To perform address reconstruction, the analysis probe stores copies of the processor's internal registers in non-volatile memory. To configure the analysis probe, the HP E2480A must be connected to an emulation module.

The general steps are:

- 1 Set the emulation module's EMSIM registers.

- **2** Load the EMSIM register values into the analysis probe.

These steps may be performed using a debugger or an HP 16600A/700A-series logic analysis system.

## To configure with a debugger

1 Configure the target processor's SIM/SCIM registers using one of the methods in Chapter 7, "Using Internal Registers (SIM and EMSIM Registers)," beginning on page 159.

You need to set the emulator copies (EMSIM registers) of the MCR, PEPAR, CSPAR0, CSPAR1, and the CSBARx and CSORx of all chip selects being used.

Using a debugger, there are two methods of configuration:

• Manually write the values into SIM/SCIM registers MCR, PEPAR, CSPAR0, CSPAR1, and the CSBARx and CSORx of all chip selects being used.

## Chapter 3: Connecting and Configuring the Analysis Probe Configuring the analysis probe for address reconstruction

- Load code into the target, perform a "reset" and "run", then perform a "break" after the SIM/SCIM registers have been configured.

- 2 Start a telnet session or open your debugger's command window.

- 3 Enter the the sync sim built-in command.

This will copy the SIM registers into the emulator's EMSIM registers.

**4** Enter the **pp** load built-in command.

This will copy the EMSIM registers into the analysis probe's non-volatile memory. The analysis probe will then be configured to properly perform address reconstruction.

## To configure with a logic analysis system

- 1 In the Emulation Control Interface, open the Configuration window.

- 2 Configure the values of the EMSIM registers using one of the methods in Chapter, "Using Internal Registers (SIM and EMSIM Registers)," beginning on page 159.

You need to set the emulator copies of the MCR, PEPAR, CSPARO, CSPAR1, and the CSBARx and CSORx of all chip selects being used.

3 Click the **Load analysis probe** button.

This sends a **pp load** command to the emulator to copy the EMSIM registers into the analysis probe's non-volatile memory.

See Also

"Using the Emulation Control Interface" on page 125.

Chapter 7, "Using Internal Registers (SIM and EMSIM Registers)," beginning on page 159.

## Configuring the Logic Analysis System

You configure the logic analyzer by loading a configuration file. The information in the configuration file includes:

- Label names and channel assignments for the logic analyzer

- Inverse assembler file name

The configuration file you use is determined by the logic analyzer you are using. The configuration file names are listed with the logic analyzer connection tables, and in a table at the end of this section.

The procedures for loading a configuration file depend on the type of logic analyzer you are using. There is one procedure for the HP 16600/700 series logic analysis systems, and another procedure for the HP 1660-series, HP 1670-series, and logic analyzer modules in an HP 16500B/C mainframe. Use the appropriate procedures for your analyzer.

# To load configuration and inverse assembler files—HP 16600/700 logic analysis systems

If you did not use Setup Assistant, you can load the configuration and inverse assembler files from the logic analysis system hard disk.

1 Click on the File Manager icon. Use File Manager to ensure that the subdirectory /hplogic/configs/hp/m683xx/E2480A/ exists.

If the above directory does not exist, you need to install the CPU32 Processor Support Package. Close File Manager, then use the procedure on the CD-ROM jacket to install the CPU32 Processor Support Package before you continue.

2 Using File Manager, select the configuration file you want to load in the /hplogic/configs/hp/m683xx/E2480A/ directory, then click Load. If you have more than one logic analyzer installed in your logic analysis system, use the Target field to select the machine you want to load.

The logic analyzer is configured for CPU32 analysis by loading the appropriate configuration file. Loading the indicated file also automatically loads the inverse assembler. The configuration file you use is determined by the logic analyzer you are using, and whether you are performing state analysis or timing analysis. The configuration file names are located at the bottom of the table showing the connections for your particular logic analyzer. They are also shown in the table on page 87.

**3** Close File Manager.

# To load configuration files—other logic analyzers

If you have an HP 1660-series, HP 1670-series, or logic analyzer modules in an HP 16500B/C mainframe use these procedures to load the configuration file and inverse assembler.

The first time you set up the logic analyzer, make a duplicate copy of the flexible disk. For information on duplicating disks, refer to the reference manual for your logic analyzer.

For logic analyzers that have a hard disk, you might want to create a directory such as CPU32 on the hard drive and copy the contents of the floppy onto the hard drive. You can then use the hard drive for loading files.

Configuring the logic analyzer consists of loading the software by inserting the floppy disk into the logic analyzer disk drive and loading the proper configuration file.

- 1 Insert the floppy disk in the front disk drive of the logic analyzer.

- **2** Go to the Flexible Disk menu.

- **3** Configure the menu to load.

- **4** Use the knob to select the appropriate configuration file.

The configuration file you use is determined by the logic analyzer you are using, and whether you are performing state analysis or timing analysis. The configuration files are shown with the logic analyzer connection tables, and are also in the table on the next page.

- **5** Select the appropriate analyzer on the menu. The HP 165xx logic analyzer modules are shown in the table on the next page.

- **6** Execute the load operation on the menu to load the file into the logic analyzer.

The logic analyzer is configured for CPU32 analysis by loading the appropriate configuration file. Loading a state configuration file also

automatically loads the inverse assembler.

7 If you are using the HP 16505A Prototype Analyzer, insert the "16505 Prototype Analyzer" flexible disk into disk drive of the prototype analyzer and update the HP 16505A from the Session Manager. You must close your workspace to run the update.

The HP 16505A Prototype Analyzer requires software version A.01.30 or higher to work with the HP E2480A.

## **Logic Analyzer Configuration Files**

| Analyzer Model      | Analyzer<br>Description<br>(Modules Only) | Configuration File for<br>Inverse Assembly | Configuration File for Timing |

|---------------------|-------------------------------------------|--------------------------------------------|-------------------------------|

| 16600A              | na                                        | C_33X_1S                                   | C_33X_1T                      |

|                     |                                           | C_37X_1S                                   | C_37X_1T                      |

| 16601A              | na                                        | C_33X_1S                                   | C_33X_1T                      |

|                     |                                           | C_37X_1S                                   | C_37X_1T                      |

| 16602A              | na                                        | C_33X_1S                                   | C_33X_1T                      |

|                     |                                           | C_37X_1S                                   | C_37X_1T                      |

| 16550A (one card)   | 100 MHz STATE                             | C_33X_1S                                   | C_33X_1T                      |

|                     | 500 MHz TIMING                            | C_37X_1S                                   | C_37X_1T                      |

| 16550A (two cards)  | 100 MHz STATE                             | C_33X_1S                                   | C_33X_1T                      |

|                     | 500 MHz TIMING                            | C_37X_1S                                   | C_37X_1T                      |

| 16554A (one card)   | 0.5M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 70/250 MHz LA                             | C_37X_2S                                   | C_37X_2T                      |

| 16555A/D (one card) | 1.0M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 110/250 MHz LA                            | C_37X_2S                                   | C_37X_2T                      |

| 16556A/D (one card) | 1.0M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 100/400 MHz LA                            | C_37X_2S                                   | C_37X_2T                      |

| 16557D (one card)   | 1.0M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 100/400 MHz LA                            | C_37X_2S                                   | C_37X_2T                      |

| 16554A (two card)   | 0.5M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 70/250 MHz LA                             | C_37X_2S                                   | C_37X_2T                      |

| 16555A/D (two card) | 1.0M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 110/250 MHz LA                            | C_37X_2S                                   | C_37X_2T                      |

| 16556A/D (two card) | 1.0M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 100/400 MHz LA                            | C_37X_2S                                   | C_37X_2T                      |

| 16557D (two card)   | 1.0M SAMPLE                               | C_33X_2S                                   | C_33X_2T                      |

|                     | 100/400 MHz LA                            | C_37X_2S                                   | C_37X_2T                      |

| 1660A/AS/C/CS/CP    | na                                        | C_33X_1S                                   | C_33X_1T                      |

|                     |                                           | C_37X_1S                                   | C_37X_1T                      |

| 1661A/AS/C/CS/CP    | na                                        | C_33X_1S                                   | C_33X_1T                      |

| 40004 /40/0/00/00   |                                           | C_37X_1S                                   | C_37X_1T                      |

| 1662A/AS/C/CS/CP    | na                                        | C_33X_1S                                   | C_33X_1T                      |

| 1070 A /D           |                                           | C_37X_1S                                   | C_37X_1T                      |

| 1670A/D             | na                                        | C_33X_2S<br>C_37X_2S                       | C_33X_2T<br>C_37X_2T          |

| 1071 A /D           |                                           | C_37X_2S<br>C_33X_2S                       |                               |

| 1671A/D             | na                                        | C_33X_2S<br>C_37X_2S                       | C_33X_2T<br>C_37X_2T          |

| 1672A/D             | no                                        | C_37X_2S<br>C_33X_2S                       | C_37X_2T<br>C_33X_2T          |

| 10/2A/D             | na                                        | C_33X_2S<br>C_37X_2S                       | C_33X_2T<br>C_37X_2T          |

|                     |                                           | U_3/A_23                                   | U_3/A_21                      |

Chapter 3: Connecting and Configuring the Analysis Probe Configuring the Logic Analysis System

Analyzing the CPU32 with a Logic Analyzer

## Analyzing the CPU32 with a Logic Analyzer

This chapter describes modes of operation for the HP E2480A analysis probe. It also describes data, symbol encodings, and information about the inverse assembler.

The information in this chapter is presented in the following sections:

- Modes of operation

- Logic analyzer configuration

- Using the inverse assembler

## **Modes of Operation**

The HP E2480A analysis probe can be used in State mode or Timing mode. The following sections describe these operating modes.

#### State mode

In State mode, the logic analyzer uses clock store qualification to capture address, data, and status information once during an instruction or data cycle. This mode is set up by the State configuration files. The State configuration files also automatically load the inverse assembler.

## Timing mode

In Timing mode, the logic analyzer samples the microcontroller pins asynchronously, at a user-selected sampling rate. The Timing mode is set up by the Timing configuration files.

State and Timing modes use different connectors on the analysis probe. The Timing pins are direct connections to the microcontroller signals. The State pins have active circuitry on the analysis probe. State information is acquired three target system clock cycles after the same information is captured in Timing mode.

## Logic Analyzer Configuration

The following sections describe the logic analyzer configuration as set up by the configuration files.

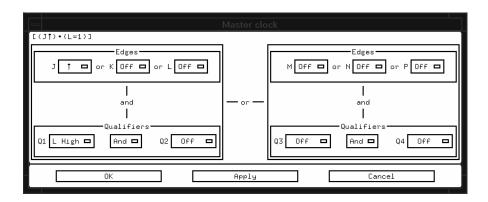

## Trigger specification

The trigger specification is set up by the software to store all states. If you modify the trigger specification to store only selected bus cycles, incorrect or incomplete disassembly may be displayed.

#### Format menu

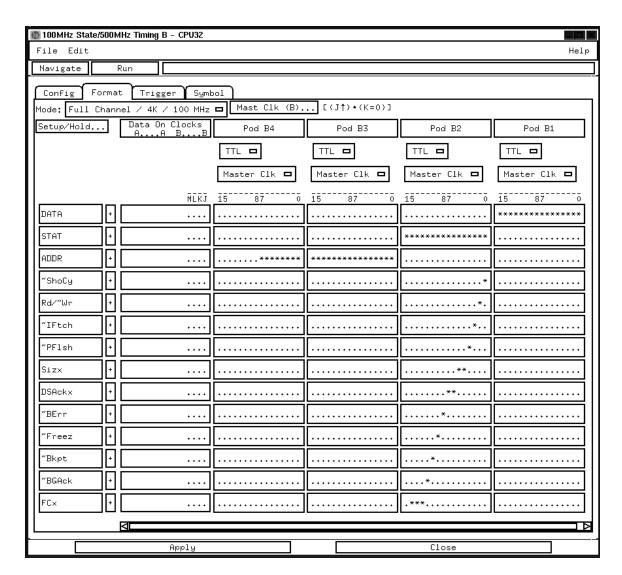

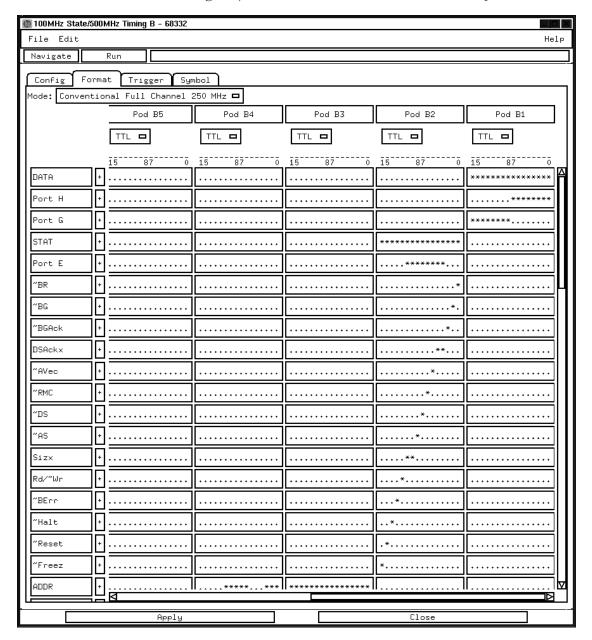

This section describes the organization of CPU32 signals in the logic analyzer's Format menu.

The configuration software sets up the analyzer format menu on the analyzer. The figure on the following page shows the Format menu for the CPU32.

The configuration files contain predefined format specifications. These format specifications include all labels for monitoring the microcontroller. The tables on the following pages show the signals used in the STAT label and the predefined symbols set up by the configuration files.

Do not modify the ADDR, DATA, or STAT labels in the format specification if you want inverse assembly. Changes to these labels may cause incorrect or incomplete inverse assembly.

#### Format Menu (State)

If fewer than eight pods are available for timing, the logic analyzer will truncate the pods allocated. In this case, the logic analyzer Format menu shows the pod allocations. If the allocations will not acquire the

# Chapter 4: Analyzing the CPU32 with a Logic Analyzer **Logic Analyzer Configuration**

desired signals, the allocations can be altered manually.

Format Menu (Timing)

#### **Status Encoding**

This section describes symbol information that has been set up by the analysis probe configuration software. The signal-to-connector tables in the "Hardware Reference" chapter list all the CPU32 signals probed and their corresponding analyzer channels.

The table below describes each of the bits of the STAT label. This table is specifically for a state configuration. The timing configurations have many of the same signals, and those signals are represented by the same symbols used for state configurations.

#### **HP E2480A STAT Bit Description**

| Bit   | STAT Label | Description                                                                       |

|-------|------------|-----------------------------------------------------------------------------------|

| 0     | ~ShoCy     | When this bit is asserted it indicates the execution of an internal (show) cycle. |

| 1     | Rd/~Wr     | Indicates the direction of the transfer.                                          |

| 2     | ~IFtch     | Indicates the bus cycle is an instruction fetch.                                  |

| 3     | ~PFlsh     | Indicates the instruction pipe has been flushed.                                  |

| 4:5   | Sizx       | Indicates the number of bytes being written or capable of being read.             |

| 6:7   | DSAckx     | Indicates the port size (in bytes) of the peripheral being read from/ written to. |

| 8     | ~BErr      | Indicates that the bus cycle terminated with an error.                            |

| 9     | ~Freeze    | When asserted, indicates the microcontroller is in background mode.               |

| 10    | ~Bkpt      | Indicates a hardware breakpoint has been encountered.                             |

| 11    | ~BGAck     | When asserted, indicates the microcontroller does not own the bus.                |

| 12:14 | FCx        | These bits indicate the area of memory with which a transfer is taking place.     |

## **Predefined Logic Analyzer Symbols**

The configuration software sets up symbol tables on the logic analyzer. The tables define a number of symbols which make several of the STAT fields easier to interpret. The following table lists the symbol descriptions.

**CPU32 Symbolic Representation of Status Bits**

| Label  | Signal      | Symbol                          | Value                |

|--------|-------------|---------------------------------|----------------------|

| ~ShoCy | ~Show_Cycle | Int<br>Ext                      | 0<br>1               |

| Rd/~Wr | Rd/~Wr      | Wr<br>Rd                        | 0<br>1               |

| ~IFtch | ~Inst_Fetch | Fetch (blank)                   | 0<br>1               |

| ~PFlsh | ~Pipe_Flush | Flush<br>(blank)                | 0<br>1               |

| Sizx   | Siz[0:1]    | long<br>byte<br>word<br>3byt    | 00<br>01<br>10<br>11 |

| DSAckx | DSAck[0:1]  | (blank)<br>word<br>byte<br>wait | 00<br>01<br>10<br>11 |

| ~BErr  | ~BErr       | Error<br>(blank)                | 0<br>1               |

| ~Freez | ~Freeze     | Bkgrnd<br>Runnin                | 0<br>1               |

Chapter 4: Analyzing the CPU32 with a Logic Analyzer **Logic Analyzer Configuration**

| Label  | Signal  | Symbol    | Value |

|--------|---------|-----------|-------|

| ~Bkpt  | ~Bkpt   | Break     | 0     |

|        |         | (blank)   | 1     |

| ~BGAck | ~BGAck  | NoBus     | 0     |

|        |         | (blank)   | 1     |

| FCx    | FC[0:2] | show      | 000   |

|        |         | user data | 001   |